# **Evaluation Board For CS4271**

#### **Features**

- Single-ended inputs

- CS8406 S/PDIF digital audio transmitter

- ◆ CS8416 S/PDIF digital audio receiver

- Header for optional external configuration of CS4271

- Header for external DSP serial audio I/O

- 3.3V to 5.0V Logic Interface

- Demonstrates recommended layout and grounding arrangements

- Microsoft Windows<sup>®</sup> compatible software interface to configure CS4271 and interboard connections

## ORDERING INFORMATION

CDB4271

**Evaluation Board**

### Description

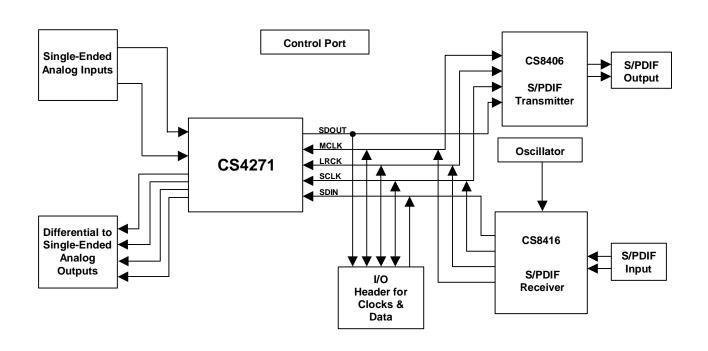

The CDB4271 demonstration board is an excellent means for evaluating the CS4271 stereo CODEC. Evaluation requires an analog/digital signal source and analyzer, and power supplies. Optionally, a Windows<sup>®</sup> PC compatible computer may be used to evaluate the CS4271 in control port mode.

System timing can be provided by the CS4271, by the CS8416 phase-locked to its S/PDIF input, by an I/O stake header or by an on-board oscillator. RCA phono jacks are provided for the CS4271 analog outputs and inputs. Digital data I/O is available via RCA phono or optical connectors to the CS8416 and CS8406.

Microsoft Windows® software provides a GUI to make configuration of the board easy. The software communicates through the PC's parallel port to configure the hardware so that all features of the CS4271 can be evaluated. The evaluation board may also be configured to accept external timing and data signals for operation in a user application during system development.

#### TABLE OF CONTENTS

| 1. | SYSTEM OVERVIEW                                | 4  |

|----|------------------------------------------------|----|

|    | 1.1 CS4272 Stereo Audio CODEC                  | 4  |

|    | 1.2 CS8406 Digital Audio Transmitter           |    |

|    | 1.3 CS8416 Digital Audio Receiver              |    |

|    | 1.4 Canned Oscillator                          |    |

|    | 1.5 Analog Input                               | 5  |

|    | 1.6 Analog Outputs                             | 5  |

|    | 1.7 Stand-Alone Control                        |    |

|    | 1.8 PC Parallel Port Control                   |    |

|    | 1.9 External Control Headers                   | 8  |

|    | 1.10 Power                                     |    |

|    | 1.11 Grounding and Power Supply Decoupling     |    |

| 2. | INITIAL BOARD SETUP                            |    |

|    | 2.1 Power Supplies:                            |    |

|    | 2.2 Installing the Software:                   |    |

|    | 2.2.1 Verifying Board Operation:               |    |

| 3. | CDB427X.EXE USER'S GUIDE                       |    |

|    | 3.1 Main Window                                |    |

|    | 3.2 Advanced Window                            |    |

|    | 3.3 I <sup>2</sup> C Mode No Acknowledge Error |    |

|    | BLOCK DIAGRAM                                  |    |

|    | SCHEMATICS AND LAYOUT                          |    |

| 6. | APPENDIX                                       | 29 |

### **Contacting Cirrus Logic Support**

For all product questions and inquiries contact a Cirrus Logic Sales Representative. To find one nearest you go to <a href="https://www.cirrus.com">www.cirrus.com</a>

#### IMPORTANT NOTICE

Cirrus Logic, Inc. and its subsidiaries ("Cirrus") believe that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability. No responsibility is assumed by Cirrus for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights associated with the information contained herein and gives consent for copies to be made of the information only for use within your organization with respect to Cirrus integrated circuits or other products of Cirrus. This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale.

An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this material and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan. An export license and/or quota needs to be obtained from the competent authorities of the Chinese Government if any of the products or technologies described in this material is subject to the PRC Foreign Trade Law and is to be exported or taken out of the PRC.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR USE IN AIRCRAFT SYSTEMS, MILITARY APPLICATIONS, PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS (INCLUDING MEDICAL DEVICES, AIRCRAFT SYSTEMS OR COMPONENTS AND PERSONAL OR AUTOMOTIVE SAFETY OR SECURITY DEVICES). INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER'S CUSTOMER OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc. All other brand and product names in this document may be trademarks or service marks of their respective owners.

I2C is a registered trademark of Philips Semiconductor. Purchase of I2C Components of Cirrus Logic, Inc., or one of its sublicensed Associated Companies conveys a license under the Philips I2C Patent Rights to use those components in a standard I2C system.

Microsoft Windows is a registered trademark of Microsoft Corporation.

# **LIST OF FIGURES**

|       | Figure 1. Instrumentation Amplifier Configuration        | 6  |

|-------|----------------------------------------------------------|----|

|       | Figure 2. Main Window                                    |    |

|       | Figure 3. Advanced Window                                |    |

|       | Figure 4. I <sup>2</sup> C Error Message                 | 14 |

|       | Figure 5. Clock and Data Routing                         |    |

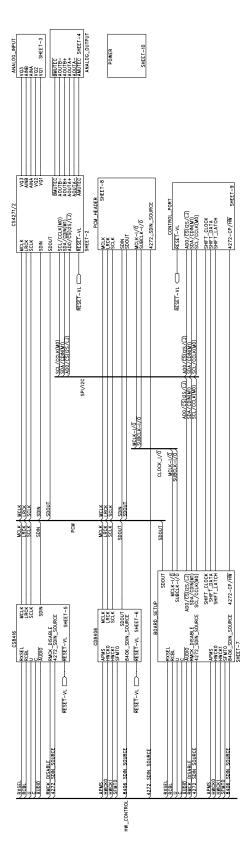

|       | Figure 6. Hierarchy, Schematic Sheet 1                   | 16 |

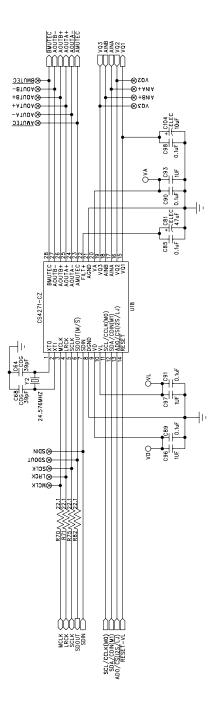

|       | Figure 7. CS4272, Schematic Sheet 2                      |    |

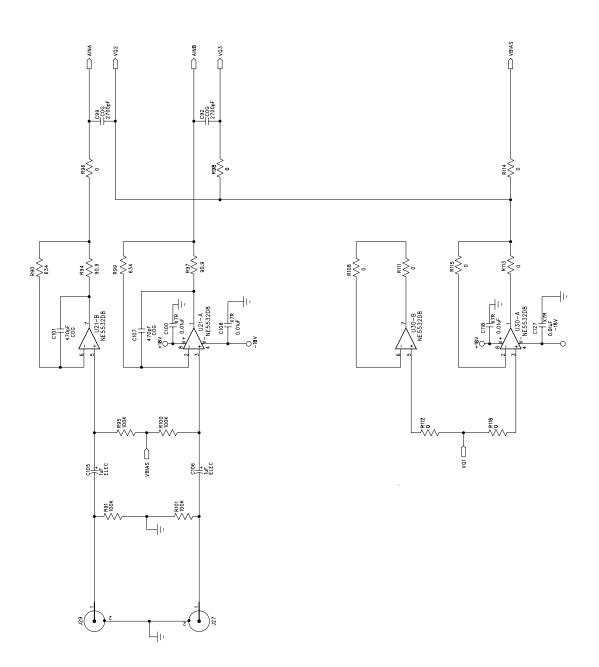

|       | Figure 8. Analog Input, Schematic Sheet 3                | 18 |

|       | Figure 9. Analog Output, Schematic Sheet 4               | 19 |

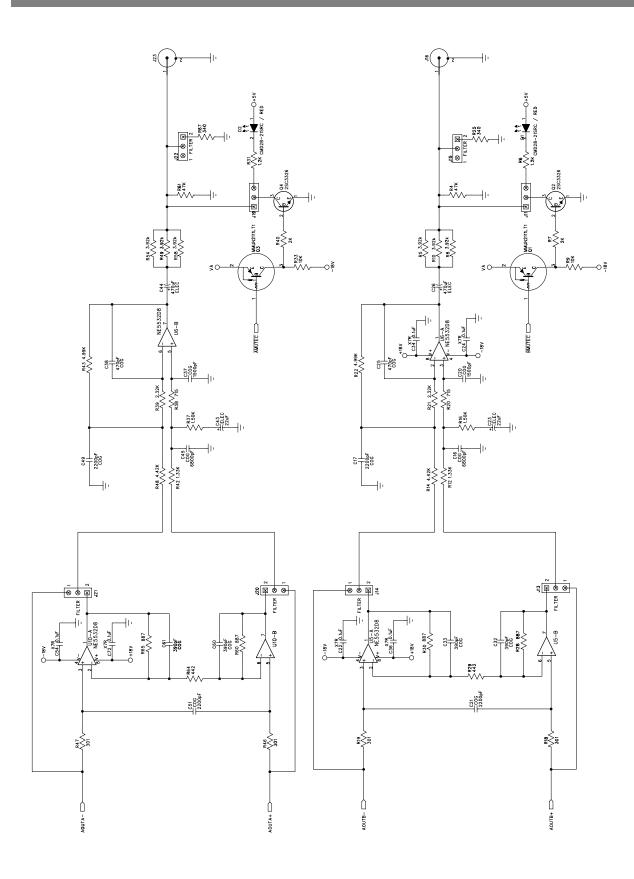

| [     | Figure 10. CS8416 S/PDIF Receiver, Schematic Sheet 5     | 20 |

|       | Figure 11. CS8406 S/PDIF Transmitter, Schematic Sheet 6  | 21 |

|       | Figure 12. Board Setup, Schematic Sheet 7                | 22 |

|       | Figure 13. PCM Header, Schematic Sheet 8                 | 23 |

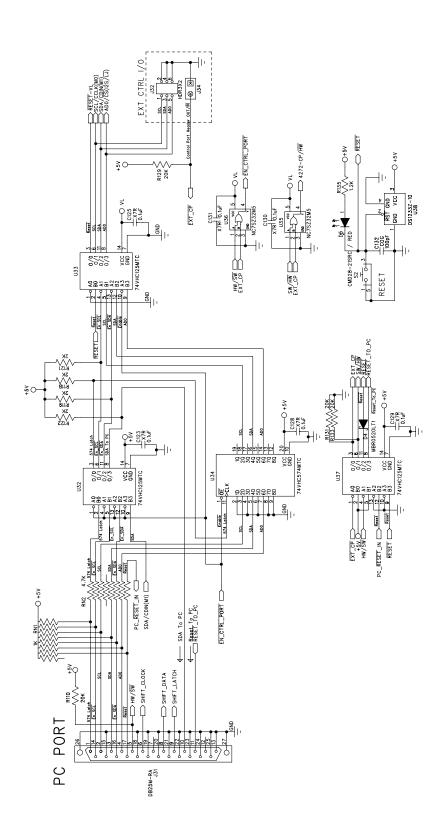

|       | Figure 14. Control Port, Schematic Sheet 9               | 24 |

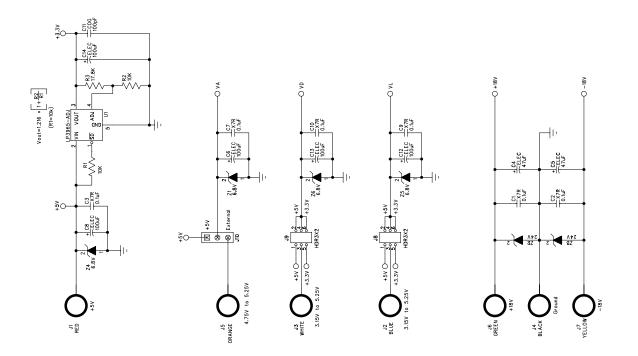

|       | Figure 15. Power, Schematic Sheet 10                     | 25 |

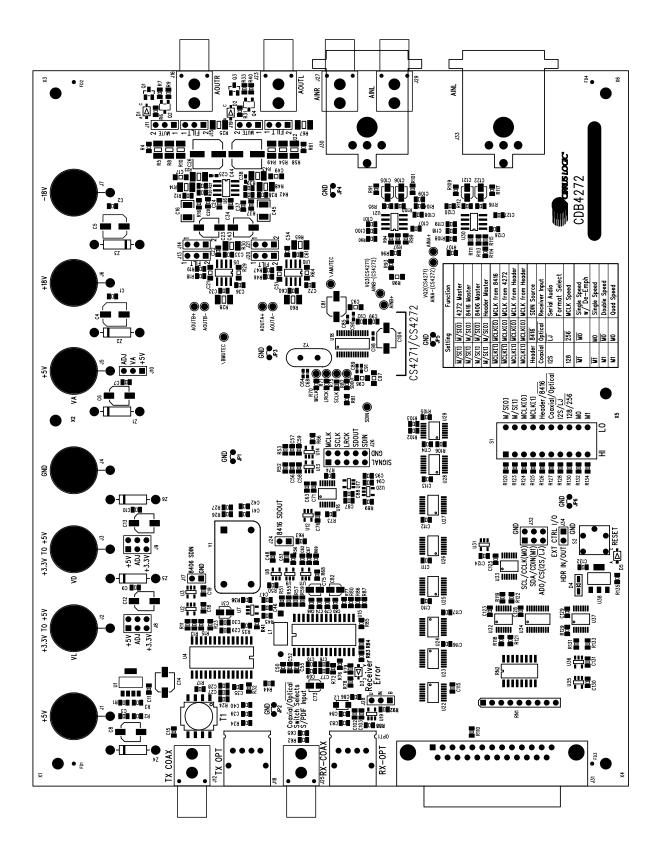

|       | Figure 16. Component Placement and Reference Designators | 26 |

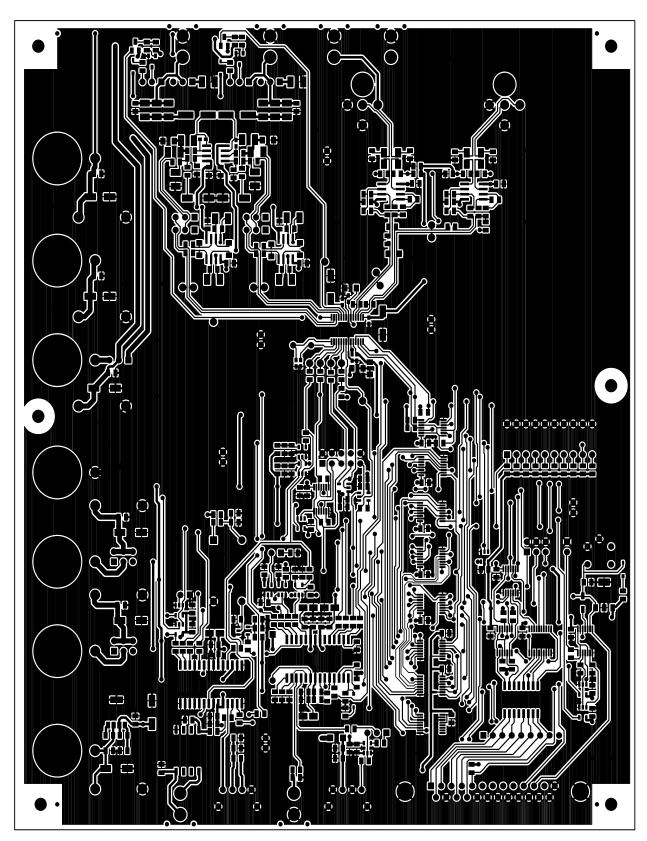

|       | Figure 17 . Top Layer                                    | 27 |

|       | Figure 18 . Bottom Layer                                 | 28 |

|       | Figure 19 . Complete Analog Input Buffer Schematic       | 29 |

|       |                                                          |    |

| IST C | OF TABLES                                                |    |

| -131  | JF IADLES                                                |    |

|       | Table 1. System Connections                              | g  |

| -     | Table 2 .lumper/Switch Settings                          | 10 |

#### 1. SYSTEM OVERVIEW

The CDB4271 demonstration board is an excellent means for evaluating the CS4271 stereo CODEC. Analog and digital audio signal interfaces are provided, as well as a DB-25 computer parallel port interface for use with the supplied Window<sup>®</sup> configuration software.

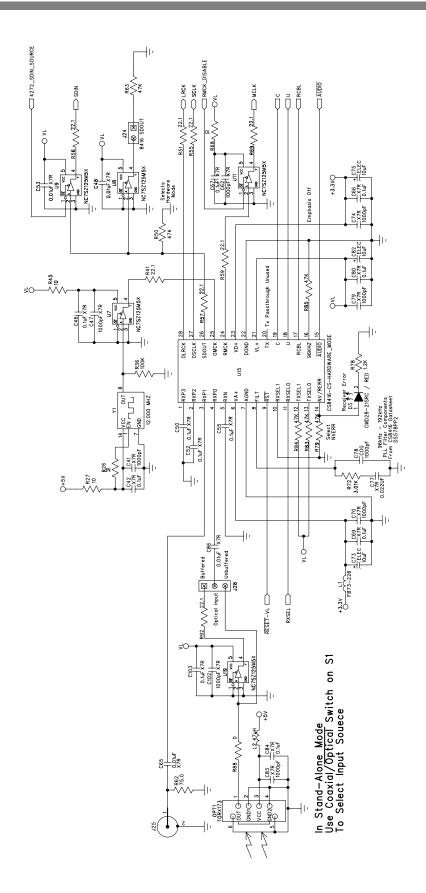

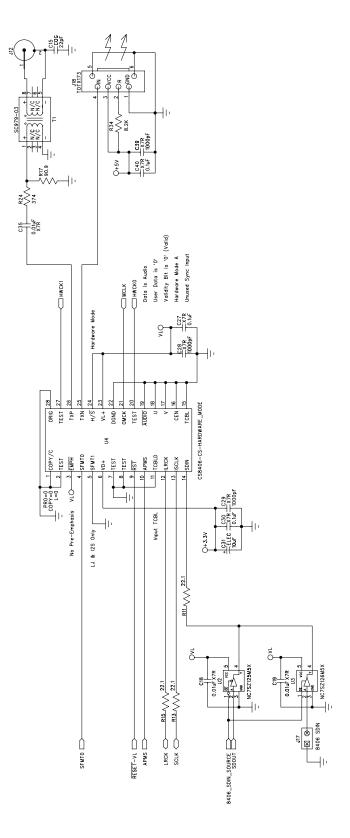

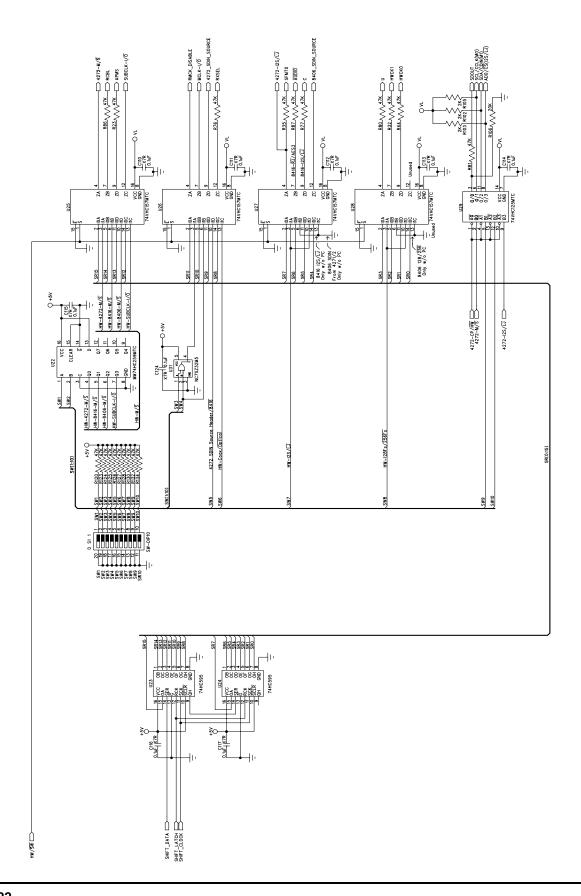

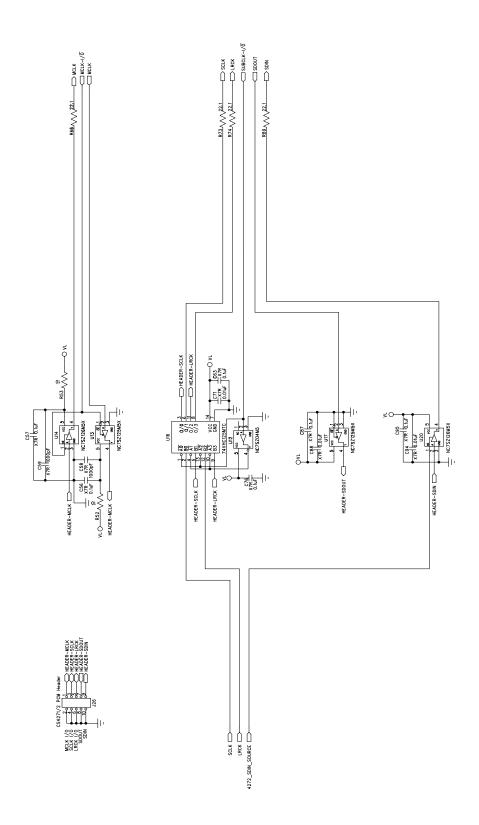

The CDB4271 schematic set has been partitioned into 10 pages and is shown in Figures 6 through 15.

#### 1.1 CS4271 Stereo Audio CODEC

A complete description of the CS4271 is included in the CS4271 product data sheet.

## 1.2 CS8406 Digital Audio Transmitter

The operation of the CS8406 transmitter (see Figure 11) and a discussion of the digital audio interface are included in the CS8406 data sheet.

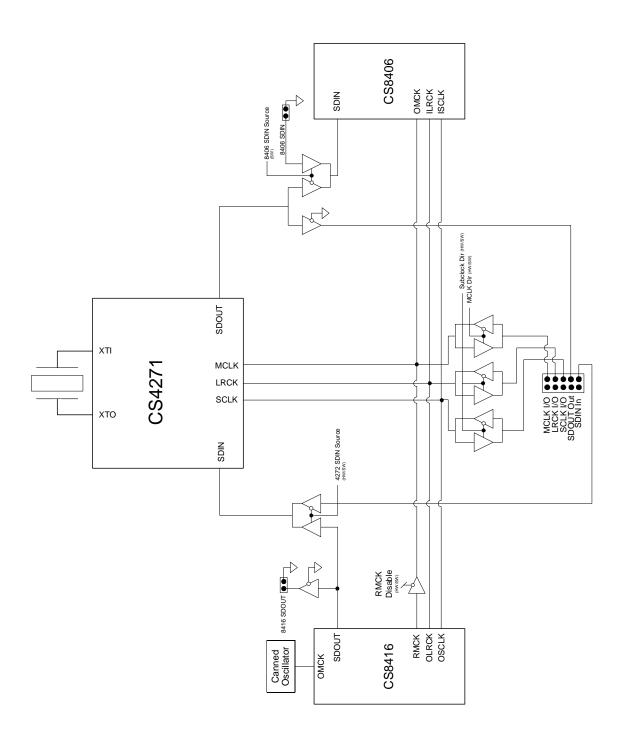

The CS8406 converts the PCM data generated by the CS4271 to the standard S/PDIF data stream. The CDB4271 is able to operate the CS8406 in either master or slave mode. The serial audio input data for the CS8406 is received from the serial audio output of the CS4271. Using the GUI, the user may elect to supply the CS8406 with an external serial audio data source through a stake header (J17). Digital Interface format selection of either Left Justified or I<sup>2</sup>S can be made via the control port GUI or via the I2S/LJ position on switch, S1 (see Table 2 for switch control options).

## 1.3 CS8416 Digital Audio Receiver

The operation of the CS8416 receiver (see Figure 10) and a discussion of the digital audio interface are included in the CS8416 data sheet.

The CS8416 converts the input S/PDIF data stream into PCM data for the CS4271. The CDB4271 is able to operate the CS8416 in master or slave mode. Digital Interface format selection of either Left Justified or I<sup>2</sup>S can be made via the I2S/LJ position on S1. Left Justified, I<sup>2</sup>S or Right Justified interface formats can be selected via the control port GUI.

The CS8416 always sources an MCLK signal. As a result, it should be noted that the CS8416 will provide invalid data in modes where the MCLK signal is generated by the CS4271 or received through the stake header (J26). Care should be taken to ensure that the crystal (Y2) is removed when the board is configured to receive MCLK from the CS8416.

The CS8416 contains an internal input multiplexer which must be set to receive the appropriate stream from the Optical or Coaxial input connector. This may be done via the Coaxial/Optical position on S1, or through the control port GUI.

#### 1.4 Canned Oscillator

Oscillator Y1 provides a System Clock (OMCK) to the CS8416. This clock can be routed through the CS8416 and out the RMCK pin by simply disconnecting the S/PDIF input. To use the canned oscillator as the source of the MCLK signal, configure the board to receive MCLK from the CS8416 using either the MCLK[1:0] positions on S1 or the GUI, and remove the input S/PDIF stream. Care should be taken to ensure that the crystal (Y2) is removed when the board is configured to receive MCLK from the canned oscillator.

The oscillator is mounted in pin sockets, allowing easy removal or replacement. The board is shipped with a 12.000 MHz crystal oscillator stuffed at Y1. Please refer to the CS8416 data sheet for details on OMCK operation.

## 1.5 Analog Input

RCA connectors supply the CS4271 analog inputs through unity gain, AC-coupled single-ended circuits. A 1 Vrms single-ended signal will drive the CS4271 inputs to full scale.

The CDB4271 was designed for use with not only the CS4271, but also the CS4272 with a simple change of assembly options. For this reason, the input buffer schematic shown in Figure 8 reflects only the configuration assembled on the CDB4271. For a complete schematic of the analog input buffer printed on the PCB, refer to the CDB4272 data sheet

### 1.6 Analog Outputs

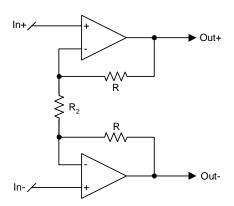

The CS4271 analog output is routed through a differential to single-ended, unity-gain low pass filter, which is AC-coupled to an RCA phono jack (see Figure 9). The analog output filter on the CDB4271 has been designed to add flexibility when evaluating the CS4271 DAC outputs. The output filter was designed in a two stage format, with the first stage being an optional instrumentation amplifier, and the second stage a 2-pole butterworth low pass filter.

The 2-pole low pass filter provides an example of an inexpensive circuit with good distortion and dynamic range performance. It is designed to have the in-band impedance matched between the positive and negative legs. It also provides a balanced to single-ended conversion for standard un-balanced outputs. Evaluate this circuit by placing the FILT jumpers (three per output channel) to position 1 (selectable by J13, J14 & J15 for AOUTR, etc.).

The instrumentation amplifier is optionally inserted before the LPF by changing the FILT jumpers to position 2. The instrumentation amplifier incorporates a 5x gain (+14 dB) which effectively lowers the noise contribution of the following 2-pole LPF. This improves the overall dynamic range of the system. The gain of this stage is determined from the following equation:

$$Gain = 1 + \frac{2(R)}{R_2}$$

The resistor designated by R2 (see Figure 1) can be adjusted to change the gain of the instrumentation amp. The feedback resistors 'R' on the two sides of the instrumentation amp must be equal.

Figure 1. Instrumentation Amplifier Configuration

A resistor divider pad (parallel combination of R5 // R8 // R10 and R22 for AOUTR) has been placed after the low pass filter to bring the circuit back to unity gain (selectable with jumper J15 for AOUTR).

In the resistor divider pad, three 3.92 k $\Omega$ , 1/4 W, 1210 size resistors are used in parallel to provide a combined resistance of 1.30 k $\Omega$  and a combined power handling of 3/4 W. This is done to provide sufficient power handling capability to accommodate the high signal levels output from the instrumentation amplifier stage. When not using the instrumentation amplifier, these resistors may be reduced to a single 1.30 k $\Omega$ , 1/10 W, 0805 size resistor (for muting attenuation purposes).

In certain places throughout the output circuit, 1/8 W, 1206 size and 1/4 W, 1210 size resistors are used. Similar to the parallel resistors in the resistor divider pad, these are used to provide sufficient power handling capability in order to accommodate the high signal levels output from the instrumentation amplifier stage. When not using the instrumentation amplifier, these resistors may all be replaced with 1/10 W, 0805 size resistors.

The attenuation provided by the output mute transistor (Q2 for AOUTR) is determined by the resistor-divider formed between the collector-emitter on-resistance and the output resistance of the LPF (R5 // R8 // R10 for AOUTR). The greater the output resistance, the greater the attenuation will be for a given transistor. The trade off is that a high output impedance is not usually desirable, and may affect the voltage transfer to the next stage based upon its input impedance.

The same resistance that affects the transistor mute level also affects the HPF formed with the output DC-block capacitor (C26 for AOUTR). For LPF configuration 2, the values for the DC-block capacitor and output resistor pad (R5 // R8 // R10 and R22 for AOUTR) were chosen to minimize the rise in distortion performance at low frequency due to the electrolytic's

dielectric absorption properties. The HPF formed by this R-C pair must be such that the voltage across the aluminum electrolytic DC-block capacitor is minimal at 20 Hz. This keeps the distortion due to the electrolytic's dielectric absorption properties to a minimum. For a design utilizing only LPF configuration 1, there is no post-LPF resistor-divider pad, and a much smaller value capacitor can be used  $(22 \, \mu F)$ .

Similar to the output DC-block capacitor described above, the value of the AC coupling capacitor from the non-inverting input of the 2-pole low pass to ground (C23 for AOUTR) was also chosen to minimize the rise in distortion performance at low frequency due to the electrolytic's dielectric absorption properties. These properties become apparent only as the signal level on that leg increases to the levels output from the differential amp used in LPF configuration 2. For a design utilizing only LPF configuration 1, the levels on that leg are sufficiently low, and a much smaller value capacitor can be used  $(22 \mu F)$ .

#### 1.7 Stand-Alone Control

Switch S1 allows stand-alone hardware signal routing and configuration of the CDB4271. See Table 2 for a list of the various options available. After changing settings using S1, the user must assert a reset by pressing the RESET button (S2).

Operation in stand-alone mode requires the parallel port cable to remain disconnected from the DB-25 connector (J31). Connecting a cable to the connector will enable the PC control port, automatically disabling switch S1 and its associated logic.

### 1.8 PC Parallel Port Control

A graphical user interface is included with the CDB4271 to allow easy manipulation of all registers of the CS4271 and hardware configuration of the CDB4271. Connecting a cable to the DB-25 connector (J31) will enable the PC control port, automatically disabling switch S1 and its associated logic.

#### 1.9 External Control Headers

The evaluation board has been designed to allow interfacing with external systems via the headers J26, J32, J17, and J24.

The 10-pin header, J26, allows the user bidirectional access to MCLK, SCLK, and LRCK. The direction of these signals is set using S1 (see Table 2 for switch control options) or the control port GUI. Also accessible from this header is a buffered version of the SDOUT signal from the CS4271, and a buffered input which, using S1 or the GUI, can be configured to drive the CS4271 SDIN pin. Care should be taken to ensure that the crystal (Y2) is removed when the board is configured to receive MCLK from this header.

The 2-pin header, J17, allows the user to supply the CS8406 with an external data source. This option is available through the control port GUI and may be asserted by setting the CS8406 data source to "Header".

The 2-pin header, J24, supplies the user with a buffered version of the SDOUT signal generated by the CS8416. This may be used, for instance, to route received S/PDIF data off-board for processing before introducing it at the SDIN position on J26.

The 6-pin header, J32, allows the user bidirectional access to the SPI/I<sup>2</sup>C control signals. The signals on J32 default to outputs. When a jumper is placed across J34, the header (J32) may be used as an input. When set as an input, the control signals on J32 are routed to the corresponding control pins on the CS4271 and external control signals may be applied.

### **1.10** Power

Power must be supplied to the evaluation board through at least three binding posts, +5.0 V (J1), +18.0 V (J6), and -18.0 V (J7). Jumper J10 allows the user to connect the VA supply of the CS4271 to a fixed +5.0 V supply or to another separate binding post (J5). Jumpers J8 and J9 connect the VL and VD supply, respectively, to a fixed +5.0 V or +3.3 V supply or to two separate binding posts (J2 and J3) for variable voltage settings. All voltage inputs must be referenced to the single black banana-type ground connector (see Figure 15).

It should be noted that devices other than the CS4271 are powered from the VL supply and therefore VL must be limited to a minimum of 3.3 V.

WARNING: Please refer to the CS4271 data sheet for allowable voltage levels.

## 1.11 Grounding and Power Supply Decoupling

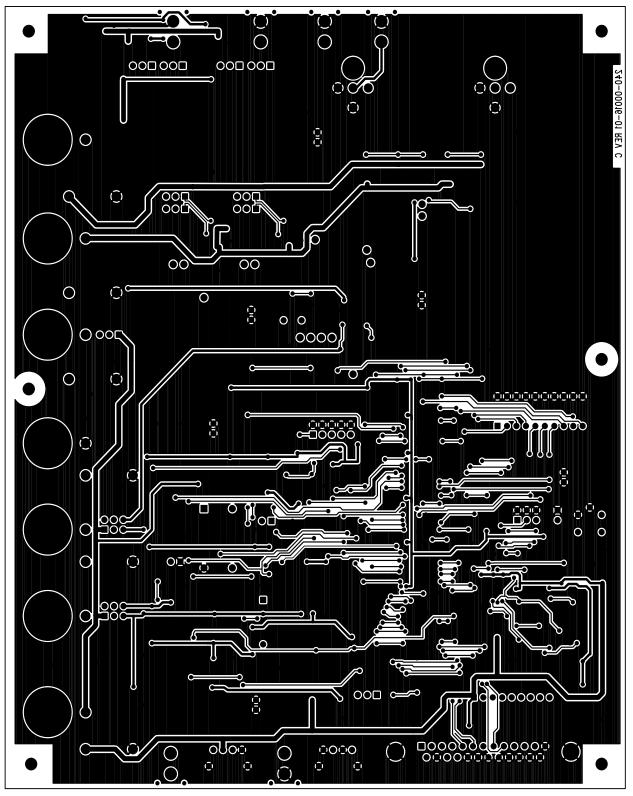

The CS4271 requires careful attention to power supply and grounding arrangements to optimize performance. Figure 5 provides an overview of the connections to the CS4271, Figure 16 shows the component placement, Figure 17 shows the top layout, and Figure 18 shows the bottom layout. The decoupling capacitors are located as close to the CS4271 as possible. Extensive use of ground plane fill in the evaluation board yields large reductions in radiated noise.

| CONNECTOR                  | INPUT/OUTPUT | SIGNAL PRESENT                                                                                                      |

|----------------------------|--------------|---------------------------------------------------------------------------------------------------------------------|

| +5V - J1                   | Input        | +5.0 V Power Supply                                                                                                 |

| -18V - J7                  | Input        | -18.0 V to -5.0 V Power Supply for the op-amps                                                                      |

| +18V - J6                  | Input        | +5.0 V to +18.0 V Power Supply for the op-amps                                                                      |

| VA - J5                    | Input        | +5.0 V Power Supply for VA                                                                                          |

| VD - J3                    | Input        | +3.3 V to +5.0 V Variable Power Supply for VD                                                                       |

| VL - J2                    | Input        | +3.3 V to +5.0 V Variable Power Supply for VL                                                                       |

| GND - J4                   | Input        | Ground Reference                                                                                                    |

| RX-COAX - J25              | Input        | Digital audio input via coaxial cable                                                                               |

| RX-OPT - OPT1              | Input        | Digital audio input via optical cable                                                                               |

| TX-COAX - J12              | Output       | CS8406 digital audio output via coaxial cable                                                                       |

| TX-OPT - J18               | Output       | CS8406 digital audio output via optical cable                                                                       |

| PC Port - J31              | Input/Output | Parallel connection to PC for SPI / I <sup>2</sup> C control port signals and system configuration                  |

| PCM HEADER - J26           | Input/Output | I/O for Clocks & Data                                                                                               |

| 8416 SDOUT - J24           | Output       | CS8416 serial data output (SDOUT)                                                                                   |

| 8406 SDIN - J17            | Input        | External data source for CS8406 SDIN                                                                                |

| EXT CTRL I/O               | Input/Output | I/O for external SPI / I <sup>2</sup> C control port signals (J32) and control signal header in/out selection (J34) |

| AINL - J29<br>AINR - J27   | Input        | RCA phono jacks for analog input signal to CS4271                                                                   |

| AOUTL - J23<br>AOUTR - J16 | Output       | RCA phono jacks for analog outputs                                                                                  |

**Table 1. System Connections**

| JUMPER /<br>SWITCH  | PURPOSE                         | POSITION | FUNCTION SELECTED                         |

|---------------------|---------------------------------|----------|-------------------------------------------|

| M/S[1:0]            | Subclock Master/Slave Select    | *00      | CS4271 is Master                          |

| (S1)                |                                 | 01       | CS8416 is Master                          |

|                     |                                 | 10       | CS8406 is Master                          |

|                     |                                 | 11       | PCM Header, J26, is Master                |

| MCLK[1:0]           | Master Clock Source Select      | *00      | CS8416 Provides MCLK                      |

| (S1)                |                                 | 01       | CS4271 Provides MCLK                      |

|                     |                                 | 10       | PCM Header, J26, Provides MCLK            |

|                     |                                 | 11       | PCM Header, J26, Provides MCLK            |

| Header/8416         | CS4271 SDIN Source Select       | *0       | CS8416 Provides SDIIN                     |

| (S1)                |                                 | 1        | PCM Header, J26, Provides SDIN            |

| Coaxial/            | Optical or Coaxial S/PDIF       | *0       | Optical Input                             |

| Optical             | Input Select                    | 1        | Coaxial Input                             |

| (S1)                |                                 |          |                                           |

| I2S/ <del>LJ</del>  | Digital Interface Format Select | *0       | Left Justified, 24-bit                    |

| (S1)                |                                 | 1        | I <sup>2</sup> S, 24-Bit                  |

| 128/ <del>256</del> | Master Clock Speed Select       | *0       | 256*Fs                                    |

| (S1)                | ·                               | 1        | 128*Fs                                    |

| M[1:0]              | CS4271 Speed Mode Select        | 00       | Single-Speed Mode, with De-emphasis       |

| (S1)                | ·                               | *01      | Single-Speed Mode, w/out De-emphasis      |

| , ,                 |                                 | 10       | Double-Speed Mode                         |

|                     |                                 | 11       | Quad-Speed Mode                           |

| J11, J19            | Selects LED or Mute Circuit for | 1        | Mute Circuit Affects Analog Output        |

|                     | AOUTA, AOUTB                    | *2       | Mute Circuit Disconnected (LED displays   |

|                     |                                 |          | xMUTEC status)                            |

| J10                 | Selects source of voltage for   | *+5V     | Voltage source is J1, +5.0 V binding post |

|                     | the VA supply                   | ADJ      | Voltage source is J5, VA binding post     |

| J9                  | Selects source of voltage for   | *+5V     | Voltage source is J1, +5V binding post    |

|                     | the VD supply                   | +3.3V    | Voltage source is +3.3 V regulator        |

|                     |                                 | ADJ      | Voltage source is J3, VD binding post     |

| J8                  | Selects source of voltage for   | *+5V     | Voltage source is J1, +5V binding post    |

|                     | the VL supplies                 | +3.3V    | Voltage source is +3.3 V regulator        |

|                     |                                 | ADJ      | Voltage source is J2, VL binding post     |

| J13, J14,           | Selects DAC Output Filter       | *1       | Selects standard 2-pole filter            |

| J15, J20,           |                                 | 2        | Inserts instrumentation-amp and resistor  |

| J21, J22            |                                 |          | divider.                                  |

\*Default factory settings

Table 2. Jumper/Switch Settings

### 2. INITIAL BOARD SETUP

## 2.1 Power Supplies:

- 1) Verify that all power supplies are off before making connections.

- 2) Connect a +5.0 VDC power supply to the +5V (J1) red binding post. If correct configuration is other than the factory default, select VL and VD operating voltage by placing a jumper on J8 and J9 to select either +5.0 V or +3.3 V.

- 3) Connect a +18.0 to +5.0 VDC power supply to the +18V (J6) green binding post. If using the FILT position number 2 for the output filter stage, +18.0 V is required on J6.

- 4) Connect a -18.0 to -5.0 VDC power supply to the -18V (J7) yellow binding post. If using the FILT position number 2 for the output filter stage, -18.0 V is required on J7.

- 5) Connect the common ground of the power supplies to the GND (J4) binding post.

- 6) Attach all required analog and digital cables to the board jacks and connectors.

- 7) If software control is desired, attach parallel port cable between board and PC.

- 8) If using the External Control Header connection, attach the required user supplied flat ribbon cable to the header with the power supplies turned off.

- 9) With all cables and connections in place, turn on the power supplies to the board. Turn on supplies in this order: +5 V, +18 V, -18 V.

- 10) Press and release the RESET switch S2. The LED, D5, will illuminate as long as S2 is depressed indicating a reset condition. Once S2 is released, the LED should turn off. If it remains on, an error has occurred. At this point, power off the power supplies and recheck all connections. Apply power to the board and press and release S2. Once the LED has turned off, the board will be setup for use.

# 2.2 Installing the Software:

- 1) Create a directory called CDB4271 anywhere on your PC.

- 2) Copy CDB427X.exe from the included CD into this directory.

- 3) Run port95nt.exe from the CD. After running the program the system will need to be restarted.

- 4) If desired, create a shortcut to CDB427X.exe on your desktop. You should now be able to run CDB427X.exe. Double-click on CDB427X.exe or its shortcut.

- 5) Select the LPT port you are using to connect to the CDB4271.

- 6) Shut down the application, reset the board, and then restart the application.

## 2.2.1 Verifying Board Operation:

- 1) If connected, disconnect the PC parallel cable.

- 2) Set all positions on S1 to LO, with the exception of M0 which should be set to HI.

- 3) Assert a reset by pressing the RESET button (S2).

- 4) Apply a S/PDIF input signal to the optical connector (OPT1). The converted signal should appear at the analog output jacks AOUTR and AOUTL.

- 5) Apply an analog input signal to the analog input jacks AINR and AINL. The converted signal should appear at the S/PDIF TX output jacks (J12 and J18).

#### 3. CDB427X.EXE USER'S GUIDE

#### 3.1 Main Window

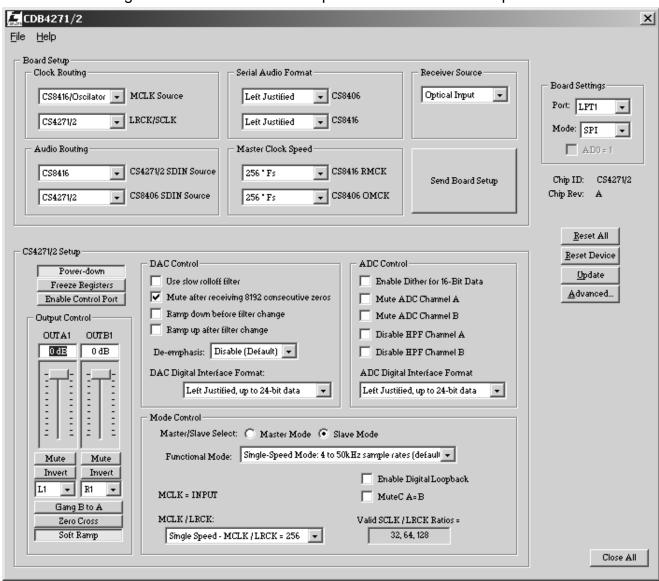

The main window of the CDB4271 Graphical User Interface allows the user to view and change the configuration of the CS4271 and on-board configuration logic.

The Board Setup box contains all the controls necessary to manage clock and data routing and formats. To apply changes to the board, the "Send Board Setup" button must be pressed after making changes within the Board Setup box.

The CS4271/2 Setup box allows configuration of the internal registers of the CS4271. Changes made within this box will be reflected immediately. When in I<sup>2</sup>C mode, the "Update" button will read the registers of the CS4271 and update the CS4271/2 Setup box to match.

Figure 2. Main Window

Clicking the "Advanced..." button will launch a graphical register map of the CS4271.

#### 3.2 Advanced Window

Clicking the "Advanced..." button on the main window will launch a graphical register map of the CS4271. Changes made to the register map will be immediately reflected in the main window, so you may wish to arrange them so that they do not obscure each other. When in I<sup>2</sup>C mode, the "Update" button will read the registers of the CS4271 and update the Advanced Register Settings box to match. See Figure 3 below.

| 900    | reserved | reserved | reserved | reserved  | reserved | reserved | reserved    | reserved    | 00 |

|--------|----------|----------|----------|-----------|----------|----------|-------------|-------------|----|

| 9 01   | М1       | М0       | Ratio1   | Ratio0    | м/з      | DAC_DIF2 | DAC_DIF1    | DAC_DIFO    | 00 |

| 902    | AMOTE    | FILT_SEL | DEM1     | DEMO      | RMP_UP   | RMP_DN   | INV_B       | INV_A       | 80 |

| g 03   | reserved | B=A      | Soft     | ZeroCross | ATAM3    | ATAM2    | ATAPI1      | ATAMO       | 29 |

| g 04   | MUTE_A   | VOL6_A   | VOL5_A   | VOL4_A    | VOL3_A   | VOL2_A   | VOLLA       | VOLO_A      | 00 |

| g 05   | MUTE_B   | VOL6_B   | VOL5_B   | VOL4_B    | VOL3_B   | VOL2_B   | VOLUB       | VOLO_B      | 00 |

| g 06 _ | reserved | reserved | Dither16 | ADC_DIF0  | MUTEB    | MOTEA    | HPPDisableB | HPPDisableA | 00 |

| 9 07   | reserved | reserved | reserved | LOOP      | MUTECA=B | FREEZE   | CPEN        | PDN         | 01 |

| 908    | reserved | reserved | reserved | reserved  | reserved | reserved | reserved    | reserved    | 00 |

| 09     | reserved | reserved | reserved | reserved  | reserved | reserved | reserved    | reserved    | 00 |

| 00     | reserved | reserved | reserved | reserved  | reserved | reserved | reserved    | reserved    | 00 |

| оь _   | reserved | reserved | reserved | reserved  | reserved | reserved | reserved    | reserved    | 00 |

| 0c _   | reserved | reserved | reserved | reserved  | reserved | reserved | reserved    | reserved    | 00 |

| 04     | reserved | reserved | reserved | reserved  | reserved | reserved | reserved    | reserved    | 00 |

| 0e   _ | reserved | reserved | reserved | reserved  | reserved | reserved | reserved    | reserved    | 00 |

| 0£     | reserved | reserved | reserved | reserved  | reserved | reserved | reserved    | reserved    | 00 |

Figure 3. Advanced Window

# 3.3 I<sup>2</sup>C Mode No Acknowledge Error

The control port of the CS4271 requires the presence of an MCLK signal for correct operation. Because of this, if the board is set up to receive MCLK from a source that isn't actively providing the signal, a no acknowledge error may result. This means that the GUI is expecting an acknowledgement from the CS4271, but isn't receiving it. If this occurs, ensure that the appropriate source of MCLK is providing the signal. For example, if the board is set up to receive MCLK from the header, be sure that there is an active MCLK signal applied to the MCLK position on the header (J26). See Figure 4 below.

Figure 4. I<sup>2</sup>C Error Message

# 4. BLOCK DIAGRAM

Figure 5. Clock and Data Routing

## 5. SCHEMATICS AND LAYOUT

Figure 6. Hierarchy, Schematic Sheet 1

Figure 7. CS4271 Schematic Sheet 2

Figure 8. Analog Input, Schematic Sheet 3

Figure 9. Analog Output, Schematic Sheet 4

Figure 10. CS8416 S/PDIF Receiver, Schematic Sheet 5

Figure 11. CS8406 S/PDIF Transmitter, Schematic Sheet 6

Figure 12. Board Setup, Schematic Sheet 7

Figure 13. PCM Header, Schematic Sheet 8

Figure 14. Control Port, Schematic Sheet 9

Figure 15. Power, Schematic Sheet 10

Figure 16. Component Placement and Reference Designators

Figure 17. Top Layer

Figure 18. Bottom Layer